Design and Manufacturing IP for USB-C/PD IC/ASICs

IQonIC Works offers a range of options for developing and integrating USB-C/PD functions on your next IC/ASIC product.

USB-C/PD IP

- Soft IP of Digital blocks

- Analog IP schematics

- Firmware

- Hard Macros

- GDS of pre-integrated IC solutions for your manufacture as standalone devices or multi-die packaged solutions (SIP)

- Finished IC. Unbranded, packaged and tested ICs to OEM.

Applications

- Source-only port

- Sink-only port

- Full DRP port

- Accessory support

- Debug support

- VCONN powered accessory or VCONN powered device

- Combination of any or all of the above

Flexible Licensing Options

- Project based, Term, or Perpetual Licenses

- Single Project or Multi-Project

- Single Technology or Multi-Project/Multi-Technology

- Manufacturing License options (GDS IP)

IP Platform

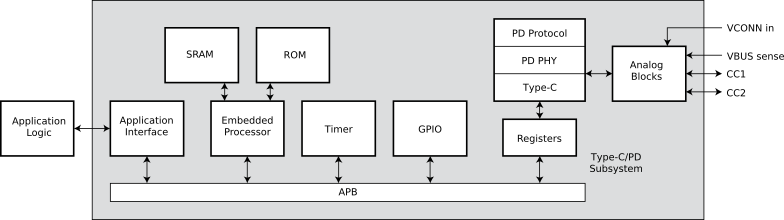

IQonIC Works offers a library of modular IP building blocks supporting a wide range of application specific solutions, including pre-integrated IQonIC Works configurations and customer own integrations.

IQonIC Works USB-C/PD IP

USB-PD functions and protocol layer implementations are available both in HW and in FW, offering a wide range of application specific integration options, including:

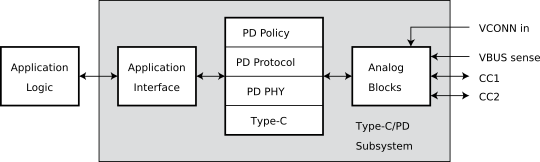

- HW only. All Type-C/PD and application functions in hardware.

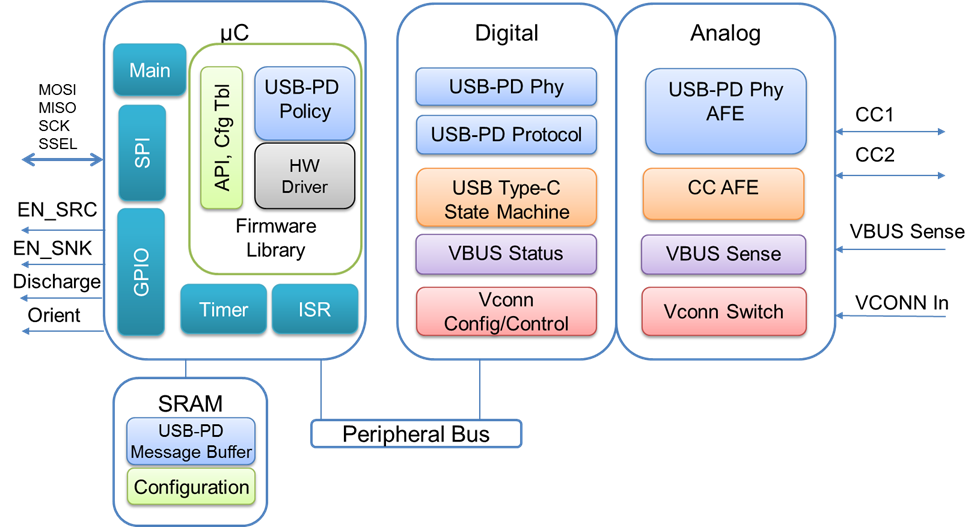

- Embedded CPU dedicated to the USB-C/PD functions. PD stack upper layers implemented in firmware, All lower level PD and Type-C functions in hardware.

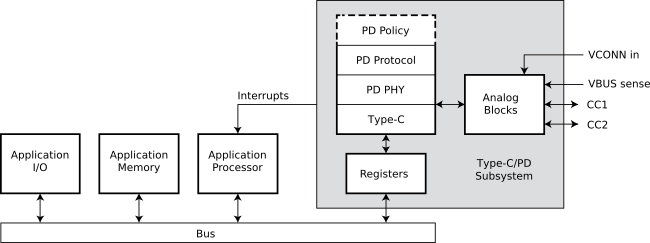

- Sharing an applications CPU for the USB-C/PD firmware and a USB-C/PD hardware block as a peripheral to the shared CPU.

Deliverables and Supporting Services

IQonIC Works provides the following deliverables in support of customer USB-C/PD needs, and can also supply a range of additional supporting IP blocks:

| Deliverables | Related IP: |

|

|

| Add-on IP: | |

|